# Guest Forum

2018堀場雅夫賞 審査委員 特別寄稿

# 原子オーダーで平坦なシリコン表面と その上に形成されたMOSデバイスの特性

Fabrication technology and characteristics of MOS device on atomically flat silicon surface

#### 寺本 章伸

#### Akinobu TERAMOTO

東北大学未来科学技術共同研究センター 教授 博士 (工学) Professor NICHe (New Industry Creation Hatchery Center) Tohoku University Ph. D.

現在、集積回路で用いられているMOSFETにおいて、シリコン表面およびゲート絶縁膜/シリコン界面の平坦 性は非常に重要であり、シリコン表面の平坦性を原子オーダーで平坦化すると信頼性が一桁以上向上し、トラ ンジスタ特性が向上することを紹介する。さらに,三次元トランジスタの導入には,シリコン結晶の面方位依存 性を理解し、使いこなす技術が重要である。三次元トランジスタを形成する際側壁面に現れるSi(110)表面で は、その表面を酸化する方法、洗浄方法、保管方法等、これまでのSi (100)表面に比べると難しくなる。そのプ ロセスについて述べるとともに、次世代のプロセスを支える計測・制御技術の課題についても述べる。

The surface roughness of silicon and interface roughness of gate insulator/Silicon are very important for MOSFETs. The lifetime of gate insulator can be one order of magnitude increased and the current drivability can be improved by the atomic order flattening compared to the conventional silicon surface. Recently, the three-dimensional MOSFET, such as "FinFET" uses Si(110) surface as the side walls. The process technologies, such as the cleaning technology, oxidation of silicon surface, transportation from an equipment to other equipment etc., of Si(110) surface is more difficult than those of Si(100) which is used for the conventional LSI's. The process technology of Si(110) and problems in the process control and measurement technologies to be solved in next generation of the integrated circuit technology are described.

#### はじめに

シリコン半導体集積回路は, Metal-Oxide-Silicon Field Effect Transistor(MOSFET)を基本的な構成素子として, その微細化によって演算処理の高速化, メモリの高集積化 等の高性能化を実現してきた。1970年代に10 μm程度の線 幅で数千個の素子を並べ、Large Scale Integrate Circuit (LSI)と呼ばれ始めた集積回路は、現在では、最小線幅が10 nmで素子数は、10億を超える。つまり、40年~50年で線幅 は,1/1000になり,集積素子数は,100万倍になっている。 この間, Central Processing Unit (CPU)の演算速度も約 1000倍に向上し、4 GHz以上で動作するものも現れている。 一方で、10 nmまで微細化されると、原子・分子レベルの 大きさに近くなり, 集積回路の高性能化を微細化だけに頼 ることには限界が見え始めている。こうした中で、様々な3 次元化によって, 性能向上が図られている。素子レベルで は、FinFET[1]と呼ばれる3次元構造のトランジスタを用い て性能向上をおこなっている。NAND型フラッシュメモリ では、メモリセルを縦方向にスタックすることにより、単 位面積あたりの集積度を向上させようとしている[2]。また.

異なる機能のLSIチップを3次元実装によって高機能化する 取り組みも行われている[3]。このような中で、半導体材料 自体をシリコンから、SiCやGaNのようなワイドバンド ギャップの半導体を用いる提案があり、パワーデバイスや 高周波デバイス等特殊な用途では、すでに実用化されてい る。しかし、高移動度のGeを含んだ材料や化合物チャネル を用いたものも含めて集積回路にはシリコン基板が用いら れており、今後も集積回路技術はシリコン基板を中心に進 められていくであろう。

本報告では,シリコン基板の表面ラフネスがデバイスに与 える影響、FinFETのような3次元デバイスになったときシ リコンの結晶面方位が変化することに対する課題を述べ る。また、これまで以上に、半導体製造プロセスには、高精 度化・高速化が求められる。そのときの制御に関する課題 を述べる。

## シリコン表面の平坦化とラフネスが MOSFETに与える影響

MOSFETの界面を流れる電子・正孔の移動度 μeffは, 以下 のような式で与えられる[4]。

$$\frac{1}{\mu_{\text{eff}}} = \frac{1}{\mu_{\text{Coulomb}}} + \frac{1}{\mu_{\text{phonon}}} + \frac{1}{\mu_{\text{roughness}}} \quad \dots \qquad \text{(1)}$$

μCoulombは、電荷散乱によって決まる移動度、μphononは格子散 乱によって決まる移動度, μroughnessは, ゲート絶縁膜とシリ コン界面ラフネスによって決まる移動度である。これらは, 印加するゲートバイアス条件によって効果が変わり, μ<sub>Coulomb</sub>, μ<sub>phonon</sub>, μ<sub>roughness</sub>の順に低電界から高電界に影響が 現れるようになる<sup>[4]</sup>。μCoulomb, μphononは, デバイスの動作条 件, 半導体基板の物性によってしか変化しないので, デバ イス構造を決めてしまうと、それほど変化しないのに対し、 μroughnessは、製造プロセスの影響を大きく受ける。このこと は、シリコン表面のラフネスを故意に大きくすることに よって、実験的にも確認されている<sup>[5,6]</sup>。1990年当時は、シ リコンウェーハのラフネスを大きくすることによってしか その効果が確認できなかったが, 近年では, 通常集積回路 製造に用いるSi(100)面においては、Arあるいは、Ar/H2中 で1100-1200℃の高温でアニールすることによって原子 オーダーで平坦化することが可能であることが見いだされ [7,8], さらに、Ar中の酸素, 水分濃度を抑制することによ

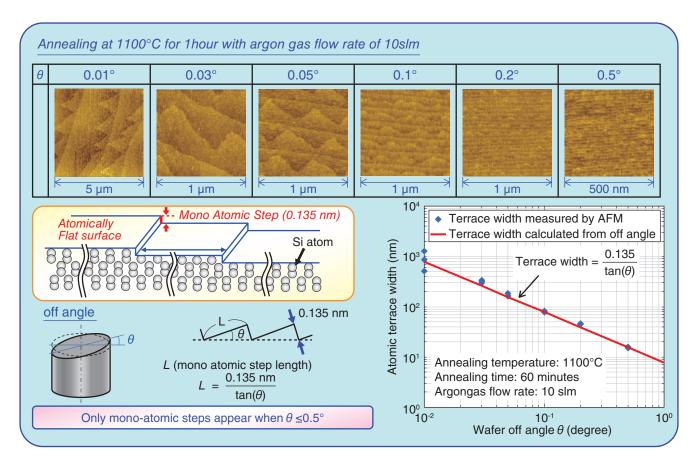

り、原子オーダー平坦化が800℃程度まで低温化できるよ うになってきた<sup>[9, 10]</sup>。このとき、Ar中に酸素、水分が存在 すると、シリコンウェーハ表面は、それらによって、エッ チングされ、却ってラフネスが大きくなってしまう[11,12]。 Figure 1には、Si (100)面について、オフ角とテラス幅の関 係を示した図とそのときのAtomic Force Microscope (AFM)像を示している[9]。ウェーハのオフ角は, X-ray Diffraction (XRD) で測定している。テラス幅Lとオフ角  $\theta$ とは、Equation 2のような関係となり、ステップの高さが 0.135 nmとSi(100)面でのSi原子一層分に相当することか ら,原子レベルで平坦化が行われていることがわかる。

$$L = \frac{0.135 \text{ nm}}{\tan \theta} \tag{2}$$

平坦なMOS界面を形成するためには、シリコン表面の平坦 化だけでなく, ゲート酸化工程までの間にシリコン表面の ラフネスを増加させてはならない。ラフネスを増加させる 要因としては, チャネルの不純物濃度を制御するためのイ オン注入, シリコン表面を直接, 水溶液に曝すウェット洗 浄. ゲート酸化そのものが挙げられる。原子オーダーで平 坦な表面のゲート酸化膜形成に通常の熱酸化を行うと,シ リコンと酸化膜の界面のラフネスは大きくなってしまう。 マイクロ波励起の低電子温度・高密度プラズマを用いた低 温ラジカル酸化を用いると、ラフネスの大きいウェーハで はシリコン/酸化膜界面は平坦化され、原子オーダー平坦

AFM images of atomically flat Si surface for various off angle from Si (100) and atomic terrace width as a function of off angle from Si (100). Only mono-atomic steps appear on the atomically flat silicon surface.

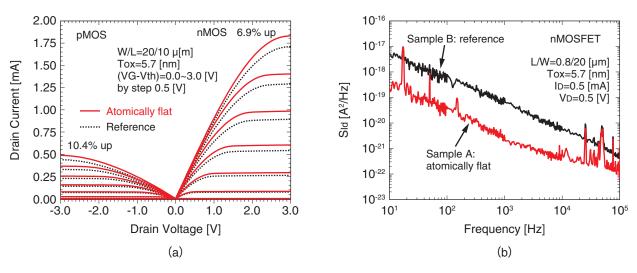

Figure 2 (a)I<sub>D</sub>-V<sub>D</sub> and (b) noise characteristics for the MOSFET with atomically flat silicon surface and conventional surface.

な表面ではそのまま原子オーダー平坦な界面が形成できる [13]。また、チャネルの不純物濃度を制御するためのイオン注入によるラフネスの増加程度であれば、ラジカル酸化で十分平坦化できるため、それを犠牲酸化として用いれば平坦性は確保できる [14]。洗浄に関しては、シリコン表面ができる限り、水溶液中に溶出しないようにする必要がある。そのためには、アルカリをできる限り用いないことと [15,16]、リンス等に用いる超純水中の酸素濃度を抑制する必要がある [17]。洗浄の際、光の影響も大きいので、遮光することも重要である [17]。

このようにして形成したMOSFETの特性を**Figure 2**に示す。(a) はドレイン電流  $(I_D)$  – ドレイン電圧  $(V_D)$  特性を示す  $[^{14]}$ 。ドレイン電圧の正側はn-MOSFETの結果,負側はp-MOSFETの結果である。基本的にMOSFETは,同じ電圧を印加したとき,より大きなドレイン電流が流れるものが高性能であるので,平坦化によって,n-MOSFETで7%,p-MOSFETで10%の性能向上ができている。(b) は

n-MOSFETの雑音特性を示している<sup>[14]</sup>。雑音電力S<sub>ID</sub>が周波数fに反比例しているので1/f雑音と呼ばれ, CMOSイメージセンサー等のアナログデバイスで大きな問題となる雑音である。平坦化することによって, 雑音電力が一桁程度低減している。p-MOSFETでも同等の効果が確認できており<sup>[18]</sup>, 平坦化は雑音低減に対し有効である。

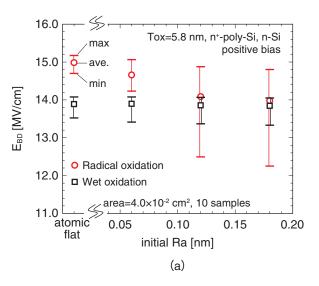

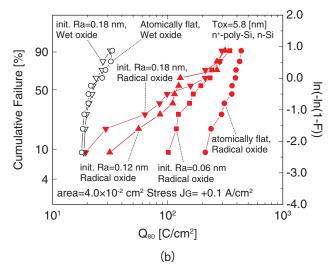

Figure 3には、酸化前のラフネスを変化させ、ゲート酸化を熱酸化、ラジカル酸化で行っている時の(a)耐圧( $E_{BD}$ )、(b)絶縁破壊電荷量( $Q_{BD}$ )を示している。熱酸化では、 $E_{BD}$ 、 $Q_{BD}$ ともラフネスの影響はほとんどなく、一定であることがわかる。これは、熱酸化では、平均表面粗さ0.1 nm程度を境目として、それよりラフネスの大きいものは平坦化され、それよりラフネスの小さなものは、ラフネスを増加させることがあるためである $^{[13]}$ 。一方で、ラジカル酸化の場合には、初期の表面ラフネス依存性が大きい。特に、ラフネスが増加するほど、低耐圧側、小破壊電荷側に裾が伸びる傾向になる。これは、ラジカル酸化に界面の平坦化効果

Figure 3 (a)E<sub>BD</sub> and (b)Q<sub>BD</sub> distribution for the gate oxides with atomically flat silicon surface and conventional surface.

があるため、ラフネスが大きな表面をイニシャルで用いる と、そのラフネスがそのままゲート電極側に残ってしまい、 結果的に大きなラフネスが残るためであると考えられる。 平坦化された表面は、ラフネスが大きなところが元々ない ために、平坦性が悪いところが、シリコン側、ゲート電極 側のどちらの界面にも存在せず、電界の集中が発生しない。 よって、表面の平坦化とラジカル酸化の組み合わせは、信 頼性を大幅に向上できることがわかる。一方で、ラフネス の大きなウェーハを用いると、初期故障が増加し、熱酸化 よりも信頼性に悪いものが出てくるため、ラジカル酸化は 用いてはならない。まとめると、熱酸化を行うのであれば、 平坦化は不必要で、やるだけ無駄であり、ラジカル酸化を 行う場合には、平坦化は必須で、組み合わせは結果として 従来技術よりも信頼性が向上する。

## 面方位が異なる場合のシリコン表面の 平坦化とその影響

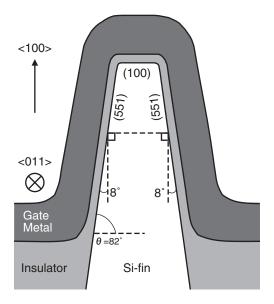

前章まではSi(100)面について、その平坦化とデバイスへの 影響を述べてきた。1章でも述べたように、近年FinFETの ような3次元トランジスタが実用化され始めており、その 場合, Si (100) 面以外の結晶面方位が現れる。2012年に発表 されたFinFETの断面写真をみるFinFETの側面は直角に 立っておらず、8°程度傾いている[19]。Figure 4にその結晶 構造<sup>[20]</sup>の解説を示した。通常のSi(100)面ウェーハを用い た場合、垂直にはSi(110)面が現れる。MOSFETの特性で 最も重要な電子, 正孔の移動度に関しては, Si (110)面, Si (551)面とも正孔はSi (100)面の3倍、電子は0.8倍程度であ る。Si(100)面は、使いやすい表面ではあるが、電子と正孔 の移動度が3倍ほど電子の方が大きいという特性がある。 通常、集積回路で用いられるCMOS構造では、電子をキャ リアとするn-MOSFETと正孔をキャリアとする p-MOSFETを直列に接続して使うため、二つの抵抗を揃え

Figure 4 Cross sectional image of FinFET and crystal structure.

るためには、移動度の小さいp-MOSFETの面積を3倍程度 にしなければならないというデメリットがあった。これに 対し、Si(110)面やSi(551)面では、二つの移動度がそれほ ど異ならないため、CMOSを構成しやすいというメリット がある。

面方位が異なると、表面の平坦化及びラフネスの増加のし やすさが異なる。平坦化の面では、先に述べたO2、H2O濃度 を低減したArアニールでは、Si (110)、Si (551) 面は平坦化 できない<sup>[21]</sup>。そこで、我々は、マイクロ波励起のXe/H<sub>2</sub>プ ラズマを用いて、400℃でSi(551)面を平坦化することに成 功した<sup>[21]</sup>。400℃という低温でも表面のマイグレーション を促進することを目的にH2を添加した。励起ガスにXeを用 いたのは、プラズマの電子温度を下げてシリコン表面への ダメージを低減するためである[22]。Si(100)面のように、原 子オーダーのステップとテラス構造は観測されないが, AFMで測定した平均荒さRaは0.068 nmとなり、原子オー ダーで平坦化されたSi (100)面と遜色ない平坦性が得られ ている。もちろん、この方法でSi(100)面も同程度に平坦化 される。一方で、表面の平坦性を維持するのも面方位に よって大きく異なる。Si (551)面は、Si (110)面に対し8°し か傾いていないが、Si(100)面に比べてもラフネスが増加し にくい[23]。

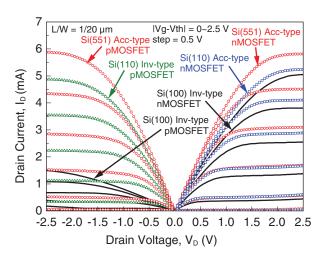

Si (110) 面は、Si (100) 面に比べてもアルカリ性溶液、超純 水に溶解しやすくラフネスが増加しやすい<sup>[24]</sup>。Figure 5は、 Si (100) 面, Si (110) 面, Si (551) 面に形成したMOSFETの ID-VD特性を示している<sup>[23]</sup>。VDが負バイアスの特性が p-MOSFET, 正バイアスの特性は, n-MOSFETを示して いる。p-MOSFETはSi(110), Si(551)面ともにSi(100)に比 べて、3倍程度のIDを得ており、高性能化されていることが わかる。n-MOSFETでもSi (100)面に比べるとIDが大きく なっているが、これは、MOSFETの構造を反転型から蓄積 型に変えたためであり<sup>[25]</sup>, 同様の構造を用いると, Si(100) 面の方が20%程度大きくなる。また、同様の構造では、Si

Figure 5 ID-VD characteristics of MOSFETs on Si(100), Si(110) and Si (551) surfaces.

(551) 面の方がSi (110) 面よりも特性がよい。これは、ゲー ト絶縁膜/シリコンの平坦性が良好であるためと考えられ る。

Figure 4で示したように、Si (551)面は、垂直から8°傾い ているため、Si (110) 面に比べて面積効率が悪い。よって、 集積度を高めるためには、Si (110)を用いた方が有利であ る。現在のFinFETは、プレーナ構造を3次元構造にしたこ とで、ゲート幅が大きくなり、その分でトランジスタ特性 が向上しているが、Si(110)表面の特性を十分発揮させるた めには、表面ラフネスを小さくするプロセスの確立が必須 である。 特に, Si (110) 面は純水中やアルカリ溶液中に溶出 しやすいため、その対策が必須である。具体的には、でき る限りアルカリ性溶液を用いないこと[16]. 光を当てないこ と, 超純水中に酸素を溶存させないこと[17], 薬液のリンス 工程で超純水にIsopropyl Alcohol (IPA)を30%程度混合 させたものを用いるのが効果的である[26]。

#### まとめと今後の課題

シリコンの平坦性とデバイスの特性について述べた。同じ シリコン結晶といっても面方位が異なるだけで, デバイス の特性が異なり、それを形成するプロセスに対する要求も 異なる。これまでは、比較的、使いやすいSi(100)面を基本 としてデバイスを形成してきたが、今後、3次元トランジス タでは、様々な面方位が現れてくる。このときにでも対応 できるプロセス技術を準備する必要がある。気相中、液相 中のプロセスとも酸素濃度が大変重要であることがわかっ た。このような、プロセス空間の雰囲気制御は大変重要に なってくる。

さらに、今後の半導体製造プロセスでは、各プロセス間の 搬送も含めた雰囲気の制御が重要になってくると考えられ る。数nmにまで微細化されたデバイス製造では、これまで のようにリソグラフィーだけにパターン制御を任せるわけ にはいかない。膜成長, エッチングプロセスに対し, 下地 に対しての選択性を強く求められている。下地との整合性 によって選択性を制御する場合,表面の分子・原子レベル の汚染は致命的になるであろう。

一方で、高精度化されたプロセスを高速に行うという要求 は常に存在する。近年, Atomic Layer Deposition(ALD), Atomic Layer Etching (ALE)といった原子オーダーのプ ロセス技術が提案され,一部実用化されている。これらは 原子オーダーの成膜、エッチングを繰り返してプロセスを 行うため、1サイクルのプロセスをできる限り短くする必 要があり、数10ミリ秒、数100ミリ秒といったプロセスス テップの制御が必要である。これを制御するためには、そ れよりも短い時間でプロセス製造装置に使われるバルブ等 は制御する必要がある。一方で、それを評価する圧力計、

ガス濃度計等には、さらなる高速化が望まれる。製造装置 内のガスは、0.1 Pa-1 kPa程度の減圧であるため、ガスの速 度は0.3-300 m/sec程度になる。ミリ秒-100 μ秒サイクルの 計測技術が必要となってくる。

今後の高性能半導体デバイス製造には、高精度なプロセス とその高速制御およびそのプロセス装置をつなぐ雰囲気制 御という基盤技術の高性能化が一層望まれる。

#### 参考文献

- [1] X. Huang, W.-C. Lee, C. Kuo, D. Hisamoto, L. Chang, J. Kedzierski, E. Anderson, H. Takeuchi, Y.-K. Choi, K. Asano, V. Subramanian, T.-J. King, J. Bokor, and C. Hu, "Sub 50-nm FinFET: PMOS," IEDM, Washington D.C., 1999, pp. 67-70.

- [2] H. Tanaka, M. Kido, K. Yahashi, M. Oomura, R. Katsumata, M. Kito, Y. Fukuzumi, M. Sato, Y. Nagata, Y. Matsuoka, Y. Iwata, H. Aochi, and A. Nitayama, "Bit Cost Scalable Technology with Punch and Plug Process for Ultra High Density Flash Memory," VLSI Technol., 2007, pp. 14-15.

- [3] 岩田剛治, "3D実装の現状と課題," スマートプロセス学会誌, vol. 4, pp. 51-54, 2015.

- [4] S. Takagi, A. Toriumi, M. Iwase, and H. Tango, "On the universality of inversion layer mobility in Si MOSFET's: Part I-effects of substrate impurity concentration," IEEE Trans. Electron Devices, 41, pp. 2357-2362, 1994.

- [5] T. Ohmi, K. Kotani, A. Teramoto, and M. Miyashita, "Dependence of electron channel mobility on Si-SiO<sub>2</sub> interface microroughness," IEEE Electron Device Letters, 12, pp. 652-654, 1991.

- [6] T. Ohmi, M. Miyashita, M. Itano, T. Imaoka, and I. Kawanabe, "Dependence of thin-oxide films quality on surface microroughness," IEEE Trans. Electron Devices, 39, pp. 537-545, 1992.

- [7] Y. Matsushita, H. Nagahama, R. Takeda, and M. Hirasawa, "Precise Control of Annealed Wafer For Nanometer Devices," ECS Trans., 3(4), pp. 159-168, 2006.

- [8] L. Zhong, A. Hojo, Y. Matsushita, Y. Aiba, K. Hayashi, R. Takeda, H. Shirai, H. Saito, J. Matsushita, and J. Yoshikawa, "Evidence of spontaneous formation of steps on silicon (100)," Phys.Rev. B, 54, R2304, 1996.

- [9] X. Li, T. Suwa, A. Teramoto, R. Kuroda, S. Sugawa, and T. Ohmi, "Atomically Flattening Technology at 850°C for Si(100) Surface," ECS Trans., 28(1), pp. 299-309, 2010.

- [10] X. Li, A. Teramoto, T. Suwa, R. Kuroda, S. Sugawa, and T. Ohmi, "Formation speed of atomically flat surface on Si(100) in ultra-pure argon," Microelectron. Eng., 88, pp. 3133-3139, 2011

- [11] M. Offenberg, M. Liehr, and G. W. Rubloff, "Surface etching and roughening in integrated processing of thermal oxides," J. Vac. Sci. Technol. A, pp. 1058-1065, 1991.

- [12] G. Ghidini and F. W. Smith, "Interaction of H2O with Si(111) and (100): Critical Conditions for the Growth of," J. Electrochem. Soc., 131, pp. 2924-2928, 1984.

- [13] R. Kuroda, A. Teramoto, X. Li, T. Suwa, S. Sugawa, and T. Ohmi, "On the Interface Flattening Effect and Gate Insulator Breakdown Characteristic of Radical Reaction Based Insulator Formation Technology," Jpn. J. Appl. Phys., 51, pp. 02BA01 1-6, 2012.

- [14] R. Kuroda, A. Teramoto, Y. Nakao, T. Suwa, M. Konda, R. Hasebe, X. Li, T. Isogai, H. Tanaka, S. Sugawa, and T. Ohmi, "Complementary Metal-Oxide-Silicon Field-Effect-Transistors Featuring Atomically Flat Gate Insulator Film/Silicon Interface," Jpn. J. Appl. Phys., 48, pp. 04C048\_1-6, Apr. 2009

- [15] T. Ohmi, "Total Room Temperature Wet Cleaning for Si Substrate Surface," J. Electrochem. Soc., 143, pp. 2957-2964, 1996

- [16] R. Hasebe, A. Teramoto, R. Kuroda, T. Suwa, S. Sugawa, and T. Ohmi, "Three-Step Room-Temperature Cleaning of Bare Silicon Surface for Radical-Reaction-Based Semiconductor Manufacturing," J. Electrochem. Soc., 156, pp. H10-H17, 2009.

- [17] H. Morinaga, K. Shimaoka, and T. Ohmi, "Impact of Light on

- the Surface Nanostructure of Silicon," J. Electrochem. Soc., 153, pp. G626-G631, 2006.

- [18] R. Kuroda, T. Suwa, A. Teramoto, R. Hasebe, S. Sugawa, and T. Ohmi, "Atomically Flat Silicon Surface and Silicon/Insulator Interface Formation Technologies for (100) Surface Orientation Large-Diameter Wafers Introducing High Performance and Low-Noise Metal-Insulator-Silicon FETs," IEEE Trans. Electron Devices, 56, pp. 291-298, 2009.

- [19] C. H. Jan, U. Bhattacharya, R. Brain, S. J. Choi, G. Curello, G. Gupta, W. Hafez, M. Jang, M. Kang, K. Komeyli, T. Leo, N. Nidhi, L. Pan, J. Park, K. Phoa, A. Rahman, C. Staus, H. Tashiro, C. Tsai, P. Vandervoorn, L. Yang, J. Y. Yeh, and P. Bai, "A 22nm SoC platform technology featuring 3-D tri-gate and high-k/metal gate, optimized for ultra low power, high performance and high density SoC applications," IEDM, San Francisco, 2012, pp. 3.1.1-3.1.4.

- [20] R. Kuroda, Y. Nakao, A. Teramoto, S. Sugawa, and T. Ohmi, "Carrier mobility characteristics of (100), (110), and (551) oriented atomically flattened Si surfaces for fin structure design of multi-gate metal-insulator-silicon field-effect transistors," Jpn. J. Appl. Phys., 53, p. 04EC04, 2014.

- [21] T. Suwa, A. Teramoto, S. Sugawa, and T. Ohmi, "Flattening Technique of (551) Silicon Surface Using Xe/H2 Plasma," ECS Trans., 61(2), pp. 401-407, 2014.

- [22] T. Ohmi, M. Hirayama, and A. Teramoto, "New era of silicon technologies due to radical reaction based semiconductor manufacturing," J. Phys. D: Appl. Phys. 39, pp. R1-R17, 2006.

- [23] W. Cheng, A. Teramoto, and T. Ohmi, "Very High Performance CMOS on Si (551) Using Radical Oxidation Technology and Accumulation-Mode SOI Device Structure," J. Electrochem. Soc., 157, pp. H389-H393, 2010.

- [24] A. Teramoto, T. Hamada, M. Yamamoto, P. Gaubert, H. Akahori, K. Nii, M. Hirayama, K. Arima, K. Endo, S. Sugawa, and T. Ohmi, "Very High Carrier Mobility for High-Performance CMOS on a Si (110) Surface," IEEE Trans. Electron Devices, 54, pp. 1438-1445, 2007.

- [25] W. Cheng, A. Teramoto, M. Hirayama, S. Sugawa, and T. Ohmi, "Impact of Improved High-Performance Si (110) -Oriented Metal-Oxide-Semiconductor Field-Effect Transistors Using Accumulation-Mode Fully Depleted Silicon-on-Insulator Devices," Jpn. J. Appl. Phys., 45, pp. 3110-3116, 2006.

- [26] M. Yamamoto, K. Nii, H. Morinaga, A. Teramoto, and T. Ohmi, "Suppression of Surface Micro-Roughness of Silicon Wafer by Addition of Alcohol into Ultra Pure Water for Rinsing Process," The 208th ECS Meeting, Los Angeles, 2005, No.758.